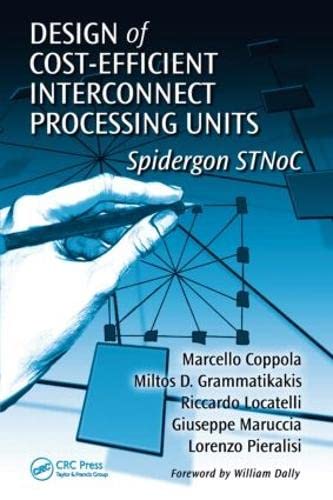

Design of Cost-Efficient Interconnect Processing Units: Spidergon STNoC (System-on-Chip Design and Technologies)

Design of Cost-Efficient Interconnect Processing Units: Spidergon STNoC (System-on-Chip Design and Technologies) is backordered and will ship as soon as it is back in stock.

Couldn't load pickup availability

Genuine Products Guarantee

Genuine Products Guarantee

We guarantee 100% genuine products, and if proven otherwise, we will compensate you with 10 times the product's cost.

Delivery and Shipping

Delivery and Shipping

Products are generally ready for dispatch within 1 day and typically reach you in 3 to 5 days.

Book Details

-

Publisher: CRC Press

-

Author: Giuseppe Maruccia, Marcello Coppola, Miltos D. Grammatikakis, Riccardo Locatelli, Lorenzo Pieralisi

-

ISBN: 9781420044713

-

Binding: Hardcover

-

Edition: 1

-

Pages: 288

-

Release Date: 17-09-2008

-

Languages: English

-

Package Dimensions: 9.3 x 6.1 x 1.0 inches

About The Book

Design of Cost-Efficient Interconnect Processing Units: Spidergon STNoC provides a comprehensive analysis of the Spidergon STNoC architecture, a cutting-edge, cost-efficient solution designed to replace traditional shared bus architectures in multiprocessor system-on-chip (SoC) applications. This book dives deep into the unique challenges and innovative solutions for on-chip network (NoC) design, a field that requires specialized techniques beyond traditional system-level network solutions.

The text explains how the SoC and NoC technologies work, their design considerations, and the tools and methodologies used to configure the Spidergon STNoC architecture. The book also compares the cost structures of NoCs with conventional system-level networks, providing valuable insights into cost-efficient design strategies.

Through numerous illustrations and simple, clear examples, the authors present theoretical and practical topics on MPSoC and NoC, including deep sub-micron technological effects, multicore SoCs, generic NoC components, and common communication pattern embeddings. This work serves as an essential resource for engineers, computer scientists, electrical engineers, and professionals in semiconductor industries interested in the future of interconnection networks for SoC applications.